UVM方法学在核安全级可编程逻辑仿真验证中的应用

|

UVM方法学在核安全级可编程逻辑仿真验证中的应用核电DCS系统中大量应用CPLD及FPGA产品,可编程逻辑产品的仿真验证是保证产品质量的重要环节。本文不同于传统的验证方法,首次将UVM验证方法应用于核安全级DCS产品可编程逻辑验证。采用独立开发的测试IP,通过灵活复用,为搭建仿真测试环境带来方便,简化了过程。采用受约束随机激励及自动检查保证测试的准确性及充分性,避免单纯用人工检查,在保证覆盖率指标的基础上,提高了测试自动化[1]水平。目前,此方法已经用于DCS系统通信路由以及优选装置的逻辑验证。

关键词:UVM方法学;核安全级;可编程逻辑;仿真验证

目录

案例背景介绍

1、 前言

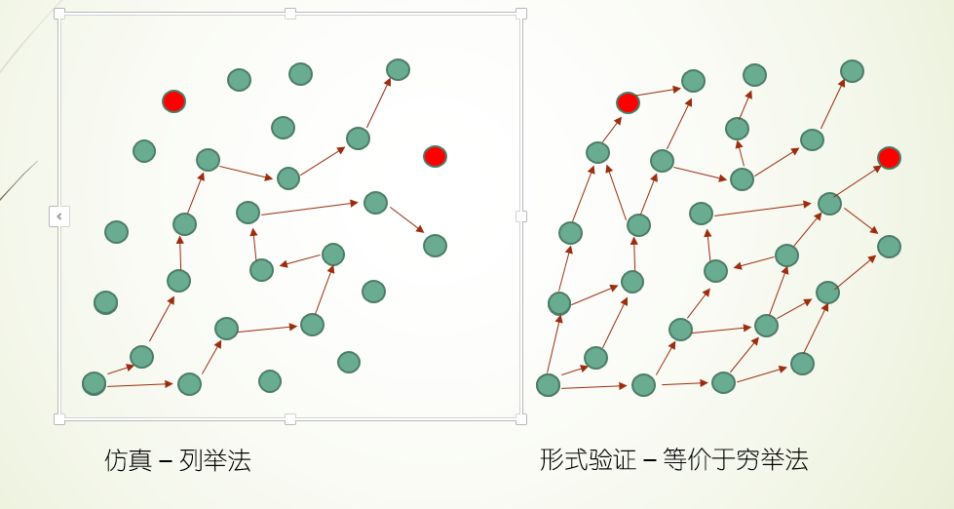

FPGA及CPLD在核电DCS领域被大量应用。可编程逻辑产品的验证是保证产品安全性、正确性的重要环节。针对可编程逻辑产品,采用行为仿真是保障产品安全性的重要验证方法。当前对于核电DCS可编程逻辑产品仿真常用的方法是先根据测试大纲编写测试用例,所有测试用例专家评审通过后,通过编写定向测试激励进行功能仿真。这种方法的局限性是针对每个测试用例都要重新编写测试环境,测试代码的更改量大,可复用性不高。

UVM (Universal Verification Methodology)是ASIC领域新兴的一种验证方法,主要用于IC芯片验证。它是一种面向对象的方法,由于它具备良好的可复用性及灵活性,UVM已经广泛用于国内外众多芯片[2]厂商。本文介绍UVM方法在DCS系统可编程逻辑产品验证中的应用。在通信路由板卡的可编程逻辑验证工作中引入UVM验证方法,在能保证与传统方法同等覆盖率指标的基础上,提高了Testbench的复用性及验证效率。

案例实施与应用情况

2、 UVM简介

UVM是IC验证业界一种新兴验证方法学,它的特点是面向对象,可复用性、扩展性好。采用UVM进行验证工作的主要优点为:

(1)UVM Testbench为模块化结构,便于验证组件复用。既可横向复用,供其它项目使用;也可纵向复用,满足同项目中更高层级的集成。

(2)UVM为达到覆盖率驱动(CDV)提供了最佳的框架。覆盖率驱动结合受约束随机激励、自动检查以及覆盖指标,可节省验证时间。

(3)采用UVM方法学便于测试维护,在不修改Testbench情况下,通过修改testcase的方式来改变测试用例,提高测试灵活性和效率。

2.1 UVM测试平台TestbenchUVM

测试平台由可复用的验证组件(verification component)构成。验证组件是封装的、易用的可配置验证环境,用于进行子模块设计、接口协议等验证。这些验证组件存储于验证人员的自开发IP组件库中,它们可以被方便的使用,在需要时根据验证人员的需求可灵活复用于多种验证环境,快速搭建起所需要的测评平台。

图1展示了一个验证环境,它由两个agent和一个vi r tualsequencer构成。每个agent验证组件遵循一致的架构,由完整的激励、检查、覆盖率统计单元集合而成。验证环境具有多路sequence机制(virtual sequencer),它将不同接口的时钟及数据同步,实现对测试环境的控制及信号激励。

2.2 UVM 类库

UVM类库以基类形式为创建新的验证组件提供标准化的可派生模板。这种类似于积木的基本构件,用户可快速开发可复用的架构、更优的验证组件及验证环境。常用的UVM类库主要基于两个典型的基类派生出来。uvm_component,用来搭建testbench架构; uvm_transaction,用于激励产生及分析。uvm_object是其共同的基类,提供uvm类的基础服务功能,例如类的创建、拷贝、克隆、显示、比较等。

参考文献

- ↑ 自动化的定义以及优缺点 ,搜狐,2019-08-14

- ↑ 什么是芯片? ,搜狐,2022-03-23